# University of Southampton

## Faculty of Engineering, Science and Mathematics School of Electronics and Computer Science

# Core Services: A new design methodology for MPSoCs

by

Dimitrios Kouzis - Loukas

September 2006

A dissertation submitted in partial fulfilment of the degree of MSc Microelectronics System Design by examination and dissertation

### **Abstract**

Significant research effort in platform based design has given numerous interesting and innovative solutions to some of the recent VLSI design automation problems. Emerging Multi-Processor System-on-Chips (MPSoC) feature reconfigurable components and hierarchical busses or Networks-on-Chips as communication infrastructure.

Core Services methodology reported in this dissertation uses mechanics inspired by Web Services that most software engineers are already familiar with to exploit efficiently dynamic partial reconfiguration and run-time mapping of current System-on-Chips (SoCs) to provide guaranteed performance increase and fault tolerance on-demand. Core services can be efficiently implemented in platforms with communication infrastructures including busses and network-on-chips.

Core Services define a function-level abstraction of the underlying hardware processing elements and a resource management mechanism (Service Broker) which optimises at run-time the mapping of functionality to available processing resources. Service Broker also measures the frequency of requests and configures reconfigurable elements to increase system's performance. Fault tolerance is considered as a resource management problem and thus solved transparently by the Core Services framework.

We validate Core Services methodology by applying it on Xilinx's reconfigurable platform for high-end FPGAs. The stack of software and hardware components for communication, data management and function virtualization is implemented and evaluated. A user-friendly application interface (API) and a powerful device driver for MontaVista embedded Linux are provided. Hardware and software components are created automatically by an easy to use platform building application able to run on Windows and UNIX workstations. The platform is being evaluated with two computationally intensive applications, AES encryption and MP3 decoding that get accelerated in different levels of granularity. We conclude by presenting our benchmarking results on a complex use case of these applications.

# **Acknowledgements**

First and foremost I would like to my supervisor Professor Bashir Al-Hashimi for his invaluable support and patient guidance during the course of this thesis.

I would also like to thank Dr. Paul Rosinger for his support on my first steps of this thesis. Our conversations gave me insights on unexplored fields and revealed interesting problems. It was a pleasure to work with you.

I dearly thank my family and my dear Eva for their never-ending love and moral support.

# **Table of contents**

| Abstract                                                           |     |

|--------------------------------------------------------------------|-----|

| Acknowledgements                                                   | III |

| Table of contents                                                  | IV  |

| List of figures                                                    | VI  |

| Chapter 1. The landscape                                           | 1   |

| 1.1 Multiprocessor System-on-chips                                 |     |

| 1.2 On-chip communication                                          |     |

| 1.3 Reconfigurable hardware                                        |     |

| 1.4 The future                                                     |     |

| Chapter 2. Introduction to Core Services                           |     |

| 2.1 Web services                                                   |     |

| 2.2 Components of a Core Services system                           |     |

| 2.3 Advantages of Core Services                                    |     |

| 2.3.1 Run-Time Mapping                                             |     |

| 2.3.2 Reconfigurable Hardware Management                           |     |

| 2.3.3 Fault tolerance                                              |     |

| 2.3.4 Platform based design                                        |     |

| 2.4 Related Work                                                   |     |

| Chapter 3. Core Services methodology, mechanics and implementation |     |

|                                                                    |     |

| 3.1 The methodology                                                |     |

| 3.2 Core Services' communication protocol and algorithms           | ۷۱  |

| 3.2.1 Phase I. Service request                                     |     |

|                                                                    |     |

| 3.2.3 Mapping algorithm                                            |     |

| 3.2.4 Reconfiguration management                                   |     |

| 3.3 Implementation issues                                          |     |

| 3.3.1 On a bus based system (CoreConnect/Amba)                     |     |

| 3.3.2 On networks-on-chip                                          |     |

| 3.4 What to make a Core Service?                                   |     |

| 3.4.1 Estimating speedup margins                                   |     |

| 3.4.2 Estimating communication overhead                            |     |

| 3.4.3 Other aspects                                                |     |

| Chapter 4. Implementation on a reconfigurable platform             |     |

| 4.1 Implementation of Core Services on Xilinx's platform           |     |

| 4.1.1 Hardware components                                          | 40  |

| 4.1.2 Linux Device Driver and the API                              | 42  |

| 4.1.3 Service Builder platform generator                           |     |

| 4.2 Applying the methodology on the two demonstration applications | 44  |

| Chapter 5. Evaluation and future work                              | 50  |

| 5.1 Benchmarking and results                                       | 50  |

| 5.2 Summary                                                        | 52  |

| 5.3 Conclusion and future work                                     | 53  |

| References                                                         | 55  |

| Appendix A. Overview of Xilinx's hardware, tools and design flows  | 62  |

| A.1 Hardware and tools overview                                    |     |

| A.2 Dynamic reconfiguration flow                                   |     |

| A.3 Montavista Linux                                               |     |

| Appendix B. Hardware entities                                      |     |

| B.1 Service Interface                                              |     |

| B.2 Service Interface                                              |     |

| B.3 Default Variable Manager                                       |     |

| B 4 Default Services                                               | 68  |

| Appendix C. Source Code                         | 68 |

|-------------------------------------------------|----|

| C.1 Reconfiguration through HWICAP              | 68 |

| C.2 rijndaelEncrypt AES encryption function     | 69 |

| C.3 synth_full mp3 decoding function            |    |

| Appendix D. Various topics                      |    |

| D.1 The checksum                                | 74 |

| D.2 I/O operation efficiency                    | 74 |

| D.3 XPS project debug and time traces           |    |

| D.4 A quick tutorial in Core Services           |    |

| Appendix E. Advanced implementation issues      | 81 |

| E.1 On networks-on-chip supporting multicasting | 81 |

| E.2 Interfacing external networks: A case study | 82 |

| Appendix F. API documentation                   |    |

| F.1 Low level API                               | 84 |

| F.2 High level API                              | 85 |

|                                                 |    |

# List of figures

| Figure 1. A System-on-Chip (Soc) featuring Network-on-Chip (NoC)                  |      |

|-----------------------------------------------------------------------------------|------|

| Figure 2. Normalized publications that include certain terms on IEEE Xplore       |      |

| Figure 3. NoC based System-on-Chip                                                | 5    |

| Figure 4. Web service's mechanics                                                 |      |

| Figure 5. A Core Service transaction                                              | 9    |

| Figure 6. Advantages of Core Services                                             | . 10 |

| Figure 7. Stating mapping                                                         | . 11 |

| Figure 8. Run-time mapping                                                        |      |

| Figure 9. Core Services' mapping                                                  |      |

| Figure 10. Reconfiguration support at current platforms                           |      |

| Figure 11. Reconfiguration management with Core Services                          |      |

| Figure 12. Fault tolerance methods                                                |      |

| Figure 13. Typical audio/ image commercial application                            |      |

| Figure 14. Fault Tolerance with Core Services                                     |      |

| Figure 15. Out of order fault tolerance with Core Services                        |      |

| Figure 16. Platform based design with Xilinx Platform Studio and MontaVista linux |      |

| Figure 17. Core Services' stack over Xilinx's Platform                            |      |

| Figure 18. Core Serices Builder: The Core Services' GUI                           |      |

| Figure 19. Core Service transaction details                                       |      |

| Figure 20. Service request packet format                                          |      |

| Figure 21. Service assignment packet format                                       |      |

| Figure 22. Request packet format                                                  |      |

| Figure 23 Response packet format                                                  |      |

| Figure 24. Free resource packet format                                            |      |

| Figure 25. Total cost for two Core Services                                       |      |

|                                                                                   |      |

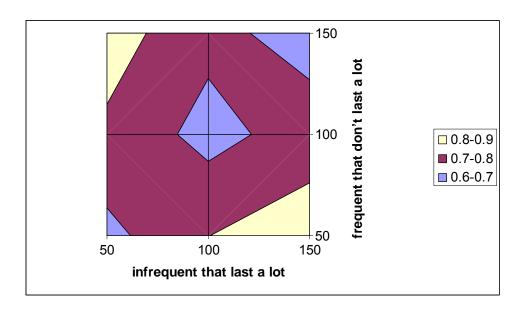

| Figure 26. A service as a two state Markov process                                |      |

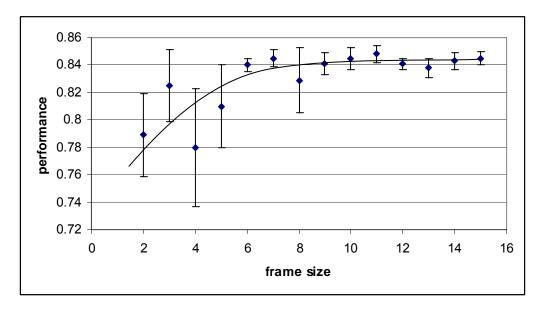

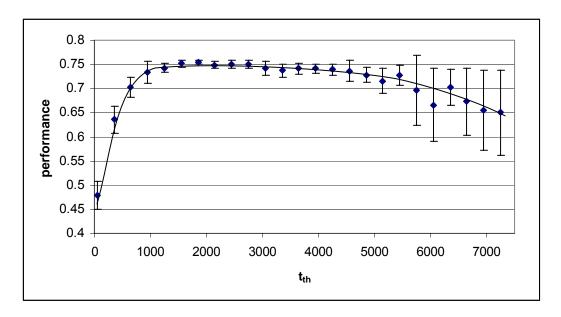

| Figure 27. Performance vs speedups  Figure 28. Performance vs frame size          |      |

| Figure 29. Performance vs frame size                                              |      |

|                                                                                   |      |

| Figure 31. Cara Cannot block diagram                                              |      |

| Figure 31. CoreConnect block diagram                                              |      |

| Figure 32. Bus-based architecture registers                                       | 34   |

| Figure 33. Core Service mechanics on bus-based architecture                       |      |

| Figure 34. Service broker status register (SBSR)                                  |      |

| Figure 35. Service broker status register (SBSR)                                  |      |

| Figure 36. IPs used by the Core Services on a NoC architecture                    |      |

| Figure 37. The Core Services' hardware stack over Xilinx's stack                  |      |

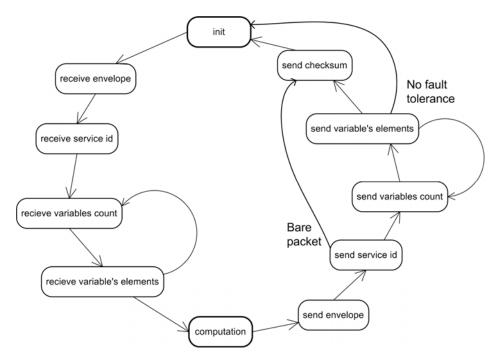

| Figure 38. The Service Interface state machine                                    |      |

| Figure 39. Default Variable Manager                                               |      |

| Figure 40. Default Services' Interface                                            |      |

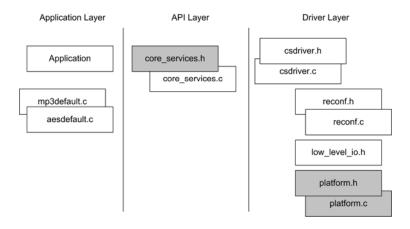

| Figure 41. Core Services' software stack                                          |      |

| Figure 42. Layers and implementation files. Shaded files are platform specific    |      |

| Figure 43. The interface provided by the Device Driver                            |      |

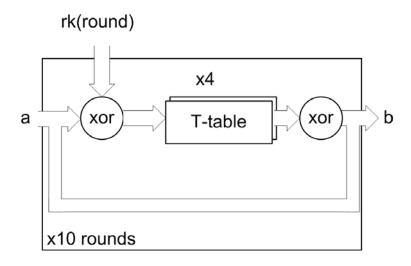

| Figure 44. AES accelerator block diagram                                          |      |

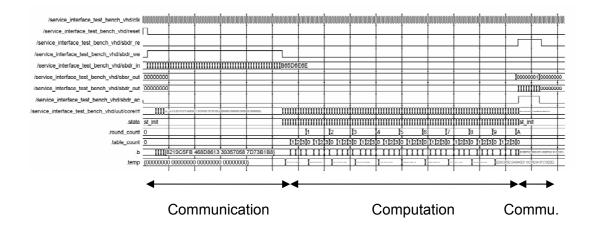

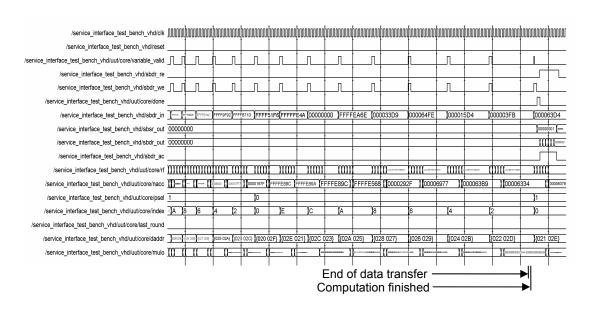

| Figure 45. Simulation of the AES accelerator                                      |      |

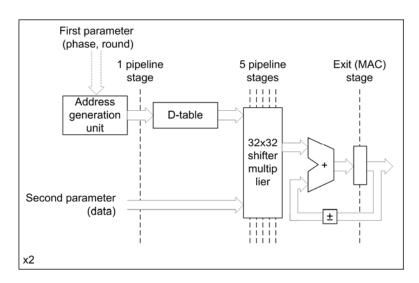

| Figure 46. MP3 accelerator block diagram                                          |      |

| Figure 47. Simulation of the MP3 accelerator                                      |      |

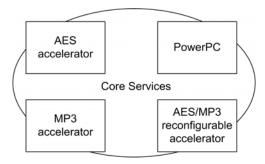

| Figure 48. Test system configuration                                              |      |

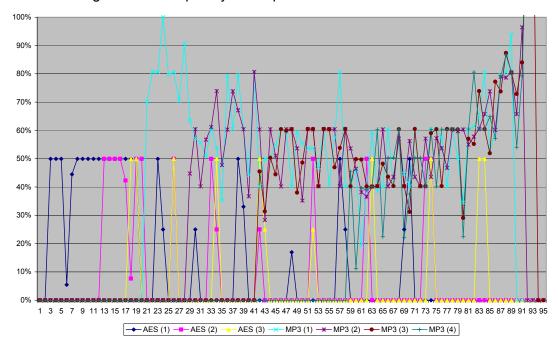

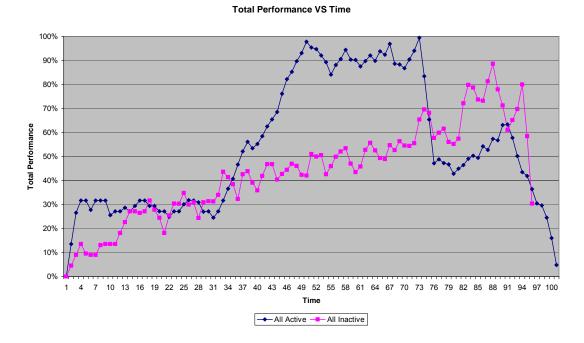

| Figure 49. Performance over time with accelerators inactive                       | 50   |

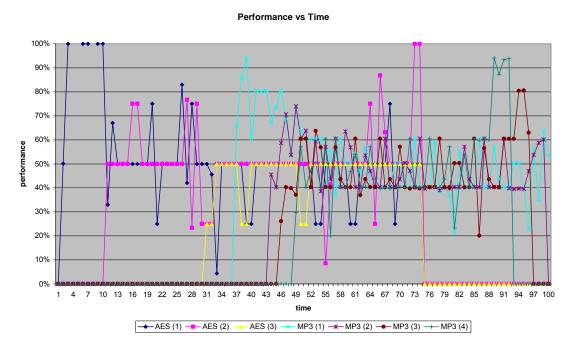

| Figure 50. Performance over time with accelerators active                         |      |

| Figure 51. System's performance with active/inactive accelerators                 |      |

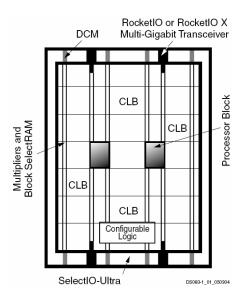

| Figure 52. Architecture overview of Virtex II Pro FPGA                            | 62   |

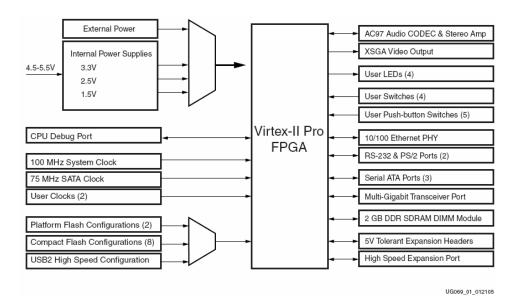

| Figure 53. System Core Diagram for the Development Board | 63 |

|----------------------------------------------------------|----|

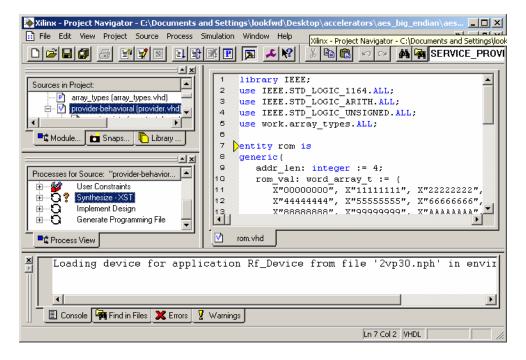

| Figure 54. Xilinx ISE development environment            | 63 |

| Figure 55. Xilinx XPS development environment            | 64 |

| Figure 56. Multicasting scheme of Core Services          | 81 |

| Figure 57. External web service request example          | 83 |

## Chapter 1. The landscape

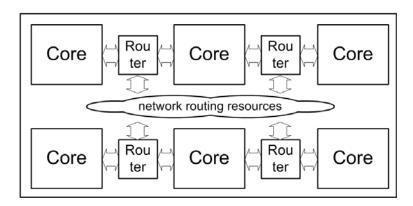

We live in the System-on-Chip (SoC) era. Complex requirements of current applications have forced VLSI design engineers to integrate multiple components on a single chip. Efficient communication between the components is challenging and has been the subject of intensive research. The Network-on-Chip (NoC) communication scheme seems promising in satisfying the communication needs of current SoCs. The structure of a modern SoC featuring NoC can be seen in Figure 1.

Figure 1. A System-on-Chip (Soc) featuring Network-on-Chip (NoC)

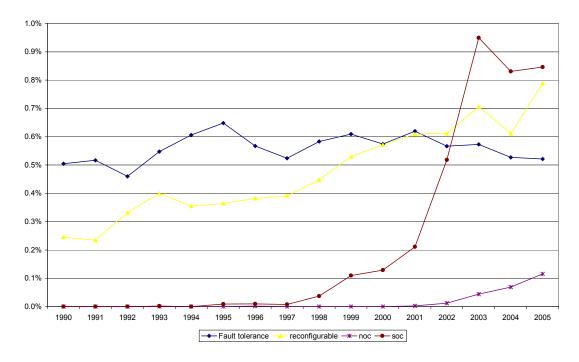

Figure 2 shows the percentage of publications that include terms used in modern VLSI design such as reconfigurable, NoC, SoC and also Fault Tolerance. This figure's data was obtained using the IEEE Xplore over the period 1990-2005.

Figure 2. Normalized publications that include certain terms on IEEE Xplore

We can see that after 2003 about 1% of the annual publications include the term "system on chip". Impressive considering the different research areas IEEE Xplore covers. The silicon integration and new opportunities that current system-on-chips

provide is the hottest topic of the first half of this decade and will probably continue to be. We can also see that there is a steady increase of publications on reconfigurability. As clock frequencies are hard to increase anymore researches are looking at reconfigurability as a means of increasing performance by transforming the performance problem from clock frequency problem to an area problem were Moore's law (see section 1.1) still holds true. We can also observe the emerging field of network-on-chips being in 2005 in about the same position where system-on-chips were in 2000. A final observation can be made for fault tolerance. For the last 15 years 0.5% of all the publications on IEEE Xplore refer to fault tolerance. The reason is the wide meaning of this word, making it useful on many contexts but clearly there is a continuous need for fault tolerant systems in all levels of Electrical and Electronics Engineering.

The key message from Figure 2 is clear. We are now designing systems-on-chip that have multiple processing elements possibly reconfigurable and in the very near future innovative designs will deploy interconnection infrastructures such as networks-on-chip. On the following sections we will present the current status of SoC design regarding the processing elements (section 1.1), communication infrastructure (section 1.2) and reconfigurability (section 1.3). We will conclude in section 1.4 with some future perspectives.

## 1.1 Multiprocessor System-on-chips

There is a constant need for integrated circuits with more processing performance and lower power consumption. At the same time it is increasingly hard to increase the operation frequency or lower the supply voltage without affecting system's reliability. The answer to these constraints seems to lie in Moore's "law" [1]; "the number of transistors on a chip duplicates every 24 months". The International Technology Roadmap for Semiconductors predicted that chips with billion transistors where within reach [2] and Montecito version of the Itanium processor already proved that in 2006 by having 1.7 billion transistors.

More transistors on a chip allow us to build complex systems optimized for certain application domains. More processing performance and lower power consumption is realized by using specialized processing elements (PEs) for tasks with different requirements. For example on a single chip a DSP algorithm can run on a DSP core, an operating system on a microprocessor and advanced video operations on custom hardware. Increased complexity makes designers face many challenging problems [3]. Power consumption increases with the number of components and may be attacked at device level [4], communication level [5] and software level [6]. The realtime constrains and performance (throughput) constrains are attacked by employing innovative heterogeneous architectures. For example instead of the standard memory hierarchy (registers, caches, external memory) employed on general purpose computational systems a MPSoCs frequently features custom memory setups including FIFOs, caches and scratchpad memories. These advanced architectures give competitive advantage on MPSoCs over traditional symmetrical multi-processor systems in terms of performance and power consumption. Security is an emerging issue for MPSoCs. Hardware and software must be designed to be secure especially in mission critical applications. This overlooked design aspect has to be given special attention since more SoC based devices are connected to public networks like the Internet. Finally, the most important problem with the increased system complexity is the ever increasing design gap. Every MPSoC requires its own suite of software tools (compilers, simulators etc.) and testing and verification becomes increasingly complex, time consuming and expensive. The solution seems

to be in design reuse with a platform based design approach which is a good choice but not a panacea [7].

### 1.2 On-chip communication

Many cores mean more communication between them and between the shared resources. This may be significant when blocks of data have to be transferred especially if they are small and frequent in which case hidden factors like handshaking and arbitization may produce significant overhead which is not visible unless detailed models of communication get used.

Many solutions have been reported to the problem of communication. Traditionally busses are employed for this purpose. An ASIC designer had to design carefully a custom set of busses to meet the bandwidth requirements of each communication path. These busses where very often bi-directional, using tri-state buffers. With higher frequencies bus design and verification became increasingly difficult because wires get longer and the inductive characteristics make transmission line effects apparent. The amount of design re-use is also limited since protocol translators (wrappers) have to be used whenever there is a change on the bus topology which costs in terms of development time and system's performance.

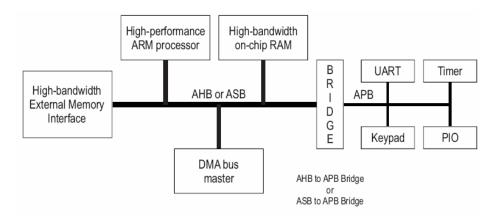

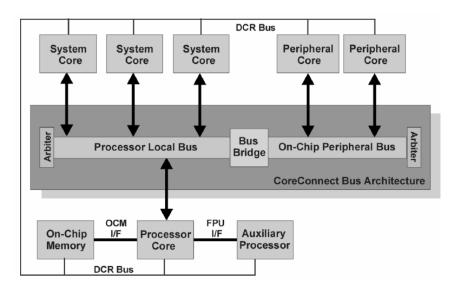

It became apparent that some standardization of the bus interfaces would benefit the ASIC industry. Three are the most standard bus interfaces at this moment. IBM's CoreConnect<sup>TM</sup> bus, ARM's AMBA bus and OpenCore's Wishbone interface. The first two come with some out-of-the-self implementations of interconnection and arbitization scheme for certain platforms while the third one leaves interconnection to the designer. CoreConnect and AMBA are both hierarchical busses featuring high performance busses for components such as memories and processors and lower performance busses for slower peripherals like communication ports. High speed buses tend to be unidirectional because bidirectional registers are hard to implement and registers are required because data transfers are pipelined in more that one bus clock cycles. High performance busses use multiplexers and have separate input and output paths that unfortunately use more wiring and area. Busses don't scale up so well because only one master can own the bus at each moment.

The successors of busses seem to be networks-on-chip. The idea of NoCs appeared at mid 2001 by the classic works of Benini and De Micheli [8, 9]. A thorough overview of the NoC technology its promises and details for two NoC implementations Xpipes and Æthereal can be found in [10] and other recent are listed in [11]. The introduction of NoCs forced designers to move from a computation-centric to a communication-centric approach. New models [12, 13] and tools [14] had to be developed to aid design exploration [15] and hw/sw co-design [16].

Network-on-Chips allow simultaneous use of chip's resources by having cores or local busses assigned to a node on an on-chip network. Nodes can communicate to each other by transferring packets of data. A response to a request from a core may take several clock cycles to arrive but it may be large enough to pay for this latency. At the same time many other cores may be taking equally large responses from other sources if there are no routing conflicts. Networks-on-chip have the potential of making better use of the increasingly expensive global wiring of a chip by utilizing less expensive routing logic. Interestingly only wishbone interface [17] mentions crossbar switch interconnections (the nucleus of every network-on-chip topology). All busses can support network-on-chip topologies via special network interfaces as seen in [18]. By issuing non-blocking memory writes on NI a master core (MC) makes requests and sends parameter data. Then MC proceeds in doing other tasks

and when the reply to his request is available on the NI it issues an interrupt to the MC in order to notify that reply data are ready. The terminal core completely abstracts the network infrastructure and gives the programmer a relatively familiar programming model if you set aside the fact that the response is asynchronous. Alternatively polling or thread suspend on a multithreading environment can give a synchronous feeling of this communication.

As NoCs is a new technology there are many unexplored fields. For example in [19] a study on the differences between battery efficiency and energy efficiency is being done for reconfigurable hardware. Battery behaviour is non-linear and the energy delivered is a function of the discharge profile. A similar study doesn't yet exist on reconfigurable NoCs. Security in NoCs is also an almost untouched field. In [20] some possible attack scenarios are being examined.

### 1.3 Reconfigurable hardware

Reconfigurable computing has received interest for more than two decades. Despite of that interest there are very few industrial applications of reconfigurable computing. As with artificial intelligence, the reason that reconfigurable computing doesn't yet seem to have produced impressive results is that it gives techniques to other research areas without being credited.

"Reconfigurable hardware is able to merge the performance of ASICs and the flexibility offered by the microprocessors" [21]. Critical software loops (kernels) can get accelerated [22, 23] by reconfiguration and at different levels of coupling between the processor and the reconfigurable fabric [24] giving different performance/energy efficiency levels in the cost of design complexity. There are various ways to categorise reconfigurable computing (for a more thorough discussion see [25]). The most widely adopted is the fine versus coarse-grained categorisation. The former is referred to our well known FPGAs which have very small reconfigurable datapaths usually 1-bit wide and a large communication mesh that can route them very flexibly. There also exist coarse-grained reconfigurable processors in the form of reconfigurable arrays (RAs) that feature reconfigurable datapaths with sizes larger that 1. These feature less configuration memory, reduced reconfiguration time and complexity of the placement and routing problem but are less flexible than fine grained solutions. In [26] and [27] numerous examples of this category are presented with details about their programming and a discussion of the software/configware partitioning problem. Nowadays we see the two categories merging as for example fine-grained FPGAs feature coarse-grained components like multipliers, DSP primitives, block rams and microprocessors but even more as their building logic blocks are becoming complex enough to model 1-4 bit ALUs.

The most important aspect of run-time reconfigurable processors that is often overlooked in the literature is that they impose, at least up to now, a large reconfiguration time during which they can't perform any computation. This creates a trade-off between how often reconfigurations are decided and the speedup that the reconfigurable hardware provides. Partial reconfiguration [28] reconfiguration time but increases complexity by giving the designer flexibility on the amount of the fabric he wishes to reconfigure. In [29] for example a two level reconfiguration scheme is presented to minimize reconfiguration time. In a mutlitrheaded [30] and even more in a multi-processor environment the use of reconfigurable PEs has to be scheduled accurately in order to maximize hardware's acceleration. Our work goes one step further by considering also communication costs into run-time reconfiguration.

Reconfigurable hardware and NoCs fit suitably well each other. The varying communication channel capacity demand of reconfigurable hardware can be addressed by dynamically reconfigurable NoC as shown in [31-33]. A comparison between this technique and dynamically reconfigurable busses is presented in [34]. Similar approaches have been examined in [35]. In [36] it is observed that NoCs would be an excellent routing resource for FPGAs and such a combined flow is presented in [37].

### 1.4 The future

The future may not hard to predict. Two different worlds; traditional computing and embedded computing are converging. The problems that computer scientists were facing a few years ago are soon going to be faced by electronic engineers. For example with multiprocessor SoCs well known problems of multithreading and computer clusters like priority inversion, convoying, deadlocks, livelocks and composability [38] are going to be faced on embedded software/hardware. Distributed databases-on-chip (DoC) over networks-on-chip may likely replace the traditional shared memory in order to attack such weaknesses and provide software developers with a familiar programming model hiding the weirdness of the underlying hardware. We already see some recent work [39-42] on the old concept of transactional memory [43, 44] and some new ideas [45].

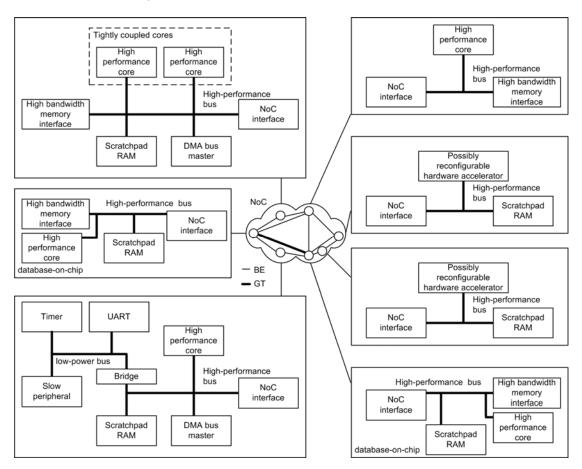

Figure 3. NoC based System-on-Chip

Although there are numerous thoughts at present now on the architectures that will be built around NoCs, the communication patterns that arise in most applications dictate topologies like the one shown in Figure 3. As we can see busses not only don't get abandoned but are used even more but they get simple (again). Increased

round-trip time of NoCs prevents them from fetching instructions on a processor and thus each core must have its own local memory at least for storing the program. The way to attack the memory bottleneck is by using multiple memory interfaces wherever needed. Tightly coupled processors are going to share the same bus while clusters of processors are going to communicate via NoC. The main communication mechanism over NoC is likely going to be Best Effort (BE) for small data packets (<8kB) and thus the buffers on routers are going to consume reasonable area. Strategically based distributed databases-on-chip are going to satisfy the shared memory requirements of cores with a safe way providing transactions and coherence protocols. The inter-processor communication using NoCs is going to be limited to message passing possibly with references on database keys. All the processors will be multi-threaded in order to take advantage of the idle time between network requests and responses.

## Chapter 2. Introduction to Core Services

In the following sections we are going to present briefly the Core Services Mechanics (section 2.2) after a short introduction to the inspiring software technology of Web Services (section 2.1). In section 2.3 we are going to present the advantages of Core Services over traditional methodologies and in section 2.4 we present related work highlighting the differences with Core Services.

### 2.1 Web services

According to the W3C [46] a Web service is a "software system designed to support interoperable machine-to-machine interaction over a network". It power lies in the flexibility it provides. A Java program can invoke Visual Basic .Net functions on the same or another PC that could run the same or another operating system. One may reasonably wonder, is this enough to make a technology such a success? The real reason that web services are a success is that companies found it as an easy way to charge for their services on a per usage basis and at the same time programmers found it reasonably easy to use. For example by using web services, Google Maps can charge a very small fee per request. If web services weren't available it should licence access to the whole GIS database to a client obviously in a much higher rate.

Clearly it would be of benefits in terms of flexibility to deal with expanding number of cores with a similar approach. For example a general purpose microprocessor running Linux could be able to invoke a function on a DSP core or an non-programmable hardware component. Actually it would be even better if we didn't have to statically refer to a component in order to invoke the function. What we want is to have the work done with the best (e.g. fastest) way and we don't really care on who exactly is the core that is going to execute it.

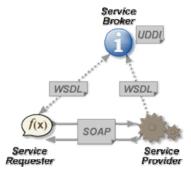

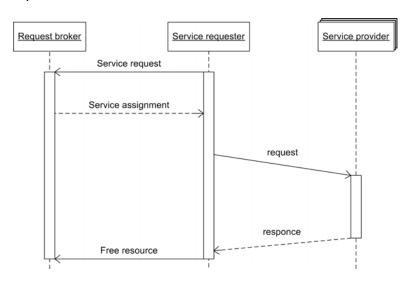

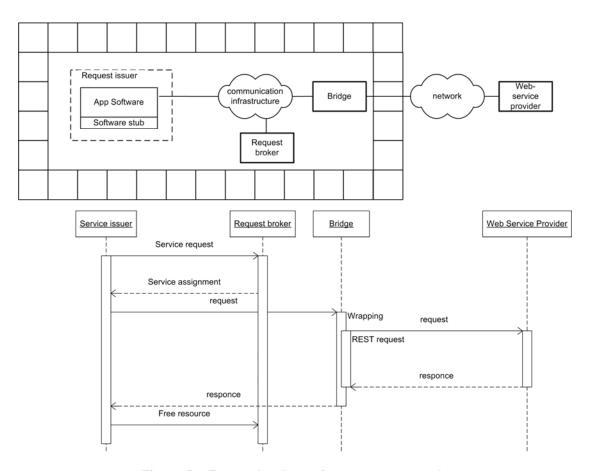

So, lets see the actual mechanics behind the web services. As you can see in Figure

4 there are three main actors for web services; the Service Provider, the Service Requester and the Service Broker. The names are self explanatory except of the Service Broker. This is a repository that holds information about web services from many providers. A service requester can query a service broker and get a list of web services that suit its needs, if available. This is the least developed part of the standard.

These actors use some protocols to achieve their goals. The service requester makes the request and gets the response by using standard web

Figure 4. Web service's mechanics

protocols like SOAP [47], XML-RPC or REST [48]. All of them are protocols based on http and use XML. An XML-RPC call for example could be an http request like this:

and a possible response could be like this:

This demonstrates the simplicity and the power of Web Services. All that is required is a web page request and response receipt using the widely supported XML format. Error handling and some primitive data types like integers, strings, structures and arrays are also provided by these protocols.

The second part of the web services functionality is achieved with WSDL [49] and UDDI [50] protocols. UDDI means "Universal Description, Discovery, and Integration" and provides the semantics for describing the needs of an application for a Web Service. That in turn returns a WSDL description of registered Web Services that satisfy these needs. UDDI mechanisms are practically used inside companies to dynamically link web services on a corporate domain.

Summarizing the two above, there are two components that are needed to make a web services interface:

- 1. A component to pass requests and get responses from a Service Provider

- 2. A component able to match Web Services to application's needs

There has been recent attempt to use reconfigurable hardware for web services [51] but obviously web services' text-based communication protocols are too heavyweight for chip level use.

## 2.2 Components of a Core Services system

We will now present the way Core Services are realized in a multiprocessor System-on-Chip. What we need is two kinds of hardware and software components as described in the previous section. In this section we will present the general characteristics for Core Services' mechanics. In order to make Core Services efficient there are many issues which are implementation specific and depend mainly on the communication infrastructure. Details for these issues for common communication schemes can be found in the section 3.3. Core Services don't define a mechanism for run-time service registration because Service availability is usually known at design time. Ad-hoc service discovery would be an overhead for most SoCs at this moment but is easy to integrate if needed.

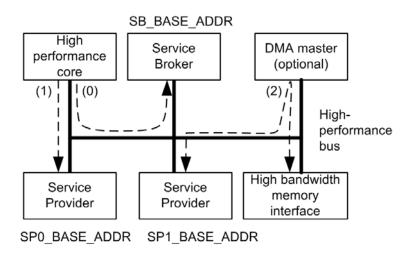

The main actors of Core Services are:

**The Service Requester**: This is a processing element that wants to offload itself or increase performance by performing a Core Service off-chip. A service requester may be running several service requests simultaneously e.g. more than one threads sleeping while waiting for services to complete.

A Service Broker: This is a processing element that manages the assignment of service provider resources to requestors. It is responsible for being up-to date with

system resources availability and allocating them with an efficient way for given performance metrics. More than one requests may be initiated from different requesters and thus an arbitration mechanism is necessary.

A Service Provider: This is a processing element that provides services. It takes the parameters from a service requester processes and sends the response back. Each service provider may provide more than one services but can serve only one request at a time. This eases the design of small embedded systems but doesn't limit larger ones because a single multi-threaded processor may implement more than one Service Providers. Information regarding the capabilities of a Service Provider is being set up on the service broker at design-time but parameters like loading may change at run-time. The service provider doesn't have to retain its state between two subsequent requests.

Figure 5. A Core Service transaction

Figure 5 gives an overview of a Core Service transaction. In the middle we can see the Service requester who initializes the transaction. On the left side the object broker analyzes the request and assigns it to an appropriate service provider which we can see in the right side. A transaction is initialized by the service requester and terminates either at the end of service assignment if there is no such service available or at the end of processing by a message to the request broker notifying that the resources are no longer used.

### 2.3 Advantages of Core Services

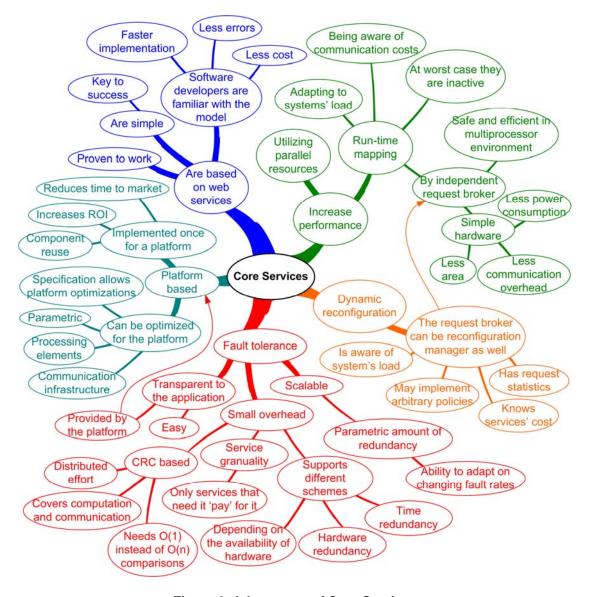

Core Services address four main problems of modern System-on-Chip design (see Figure 6):

- 1. Run-Time Mapping

- 2. Reconfigurable Hardware Management

- 3. Fault tolerance

- 4. Platform based design

Figure 6. Advantages of Core Services

We will examine these problems, the way that others solve it and what advantages Chip Services provide over other methods in the following sections.

### 2.3.1 Run-Time Mapping

Traditionally static methods [52, 53] have been used for mapping communication transactions and computation tasks to PEs. In practice [54] mapping distributed applications into NoC architectures is quite difficult even with simple static mapping if the application is not designed for the platform at first place. Many studies have been done in static mapping for minimum energy consumption with realtime constraints by using linear programming [55] evolutionary [56] and other [57-59] algorithms.

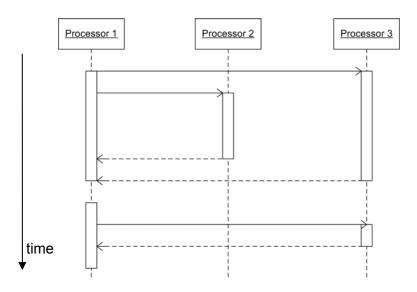

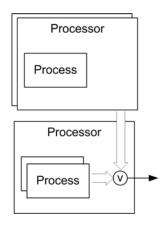

Figure 7. Stating mapping

In Figure 7 we can see an execution scenario with static scheduling. Processor 1 is master and initializes two tasks in slave processors Processor 2 and 3. All of them run in parallel and when they all complete the master Processor 1 returns the function results and is free to start another function e.g. by initializing another task in Processor 3. Stating mapping creates a static schedule on the processing elements of a system. This is being obtained via profiling and defines the performance and the power efficiency of the system.

Run-time mapping has recently started being investigated. In [60, 61] they propose use-cases to reconfigure the network more efficiently, an idea that is also employed in [62]. Generally, reconfiguring the network [63] seems to be the preferred way to reduce network contention and provide fault tolerance [64-66].

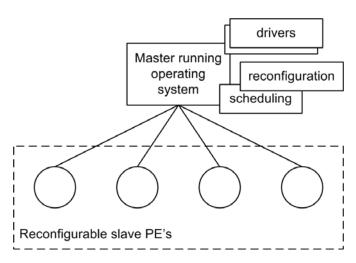

Figure 8. Run-time mapping

As we can see in Figure 8 run-time mapping schedules operations at run time taking into account the computation and communication loads. By scheduling at run-time the system can perform optimally under several different use cases in contrast to static scheduling. As Peng Yang et al. discuss [62] modern standards like e.g. MPEG21 and MPEG4/JPEG2000 execute code based on non-deterministic events and as a result design-time mapping is unable to provide optimum performance. Run time mapping usually employs a scheme where a master processor uses an operating system to profile the system and schedule tasks on slave processors.

Both static and run-time scheduling won't scale well in future MPSoCs because they feature multiple equivalent masters that have to compete for the same accelerating

resources. In order to improve the system's performance we need to accelerate ondemand all the masters.

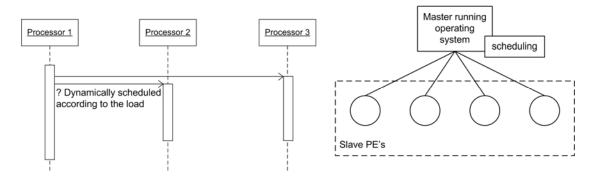

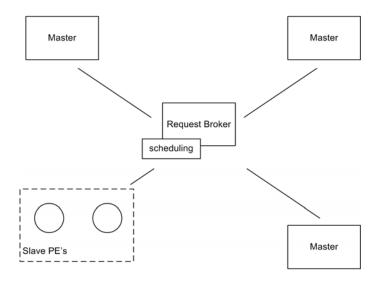

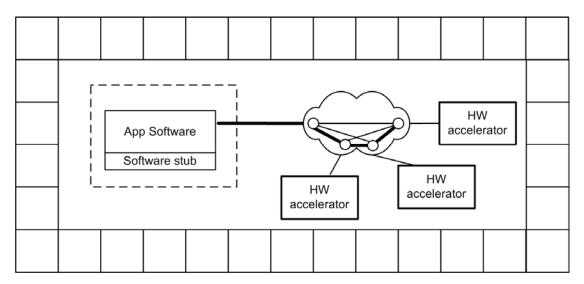

Figure 9. Core Services' mapping

Core Services are designed for these systems. As we can see in Figure 9 the requests from multiple masters are being processed by a centralized scheduler mechanism, the Request Broker. It is trying to optimise system's performance by mapping functionality to Slave PE's (Service Providers). It must be noted that a master processor may also provide services and thus invoke calls into itself.

### 2.3.2 Reconfigurable Hardware Management

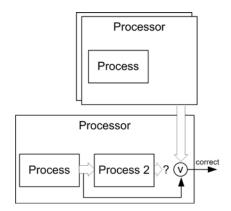

There are two main problems with reconfigurable hardware. The first one is the communication between reconfigurable components and the second one is when to decide reconfiguration. A master device must be able to communicate with the reconfigurable component independently of its current configuration. This requires a level of communication abstraction. Also alternatives of reconfigurable component's functionality must be available in order to address the unavailability of the reconfigurable processing element during reconfiguration. Finally the decision of reconfiguration should be made according to the current processing needs of the application.

Figure 10. Reconfiguration support at current platforms

All these problems are being addressed with a very Ad-Hoc manner at this moment [30, 67-69]. Communication with reconfigurable components is being done by having several different drivers and using one of them according to the current configuration. The alternative implementation during reconfiguration is usually addressed at application level. Also reconfiguration is being decided based on the demands of a single processor and runs in parallel with the scheduler on the operating system.

Core Services were developed while working on a reconfiguration problem. The problem of abstracting functionality that because of reconfiguration sometimes exists and others not leaded to a run-time mapping solution.

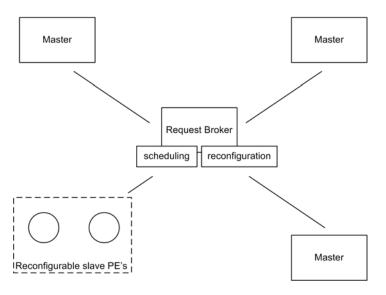

Figure 11. Reconfiguration management with Core Services

As we can see in Figure 11 the request broker has already all the information needed to decide efficiently and transparently if a reconfiguration is needed. It knows the demand for each Core Service and the performance gains if it was available on one or more reconfigurable components. The most important is that by using the Request Broker for reconfiguration management the whole system can be totally unaware of the existence of reconfiguration. It's completely hidden behind the Core Services' Applications Interface (API) and provides optimum hardware acceleration. Operating systems (such as Linux) can be used for Masters without the need of customizations. An additional advantage is that the reconfiguration management can be done in a non application specific manner and thus reused over designs. This is a very important benefit of the Core Services' mechanism.

### 2.3.3 Fault tolerance

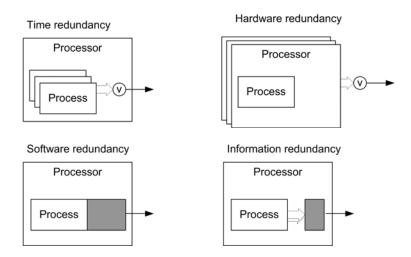

Fault-tolerance allows a system to continue operating properly when some of its components fail [70]. The main problem with VLSI systems is to ensure transient fault-tolerance which means tolerance to Single Event Upsets (SEUs) [71]. Fault tolerance is traditionally being enhanced with the following four methods (Figure 12):

- a) Time redundancy: A single function is being executed more than once and the results are compared. This is very popular technique since it requires less hardware/software resources but a multiple of the original time of the function is being used decreasing performance.

- b) Hardware redundancy. In contrast to time redundancy, this technique uses a large number of modules each one executing the same function and their results are being

compared. Obviously this requires a lot of extra resources but it can achieve increased performance.

Figure 12. Fault tolerance methods

- c) Software redundancy: In this approach sanity tests are being applied to the output data in order to verify that they are correct. This requires extra time but less than time redundancy technique. The fault tolerance techniques of this kind are highly application dependent and can hardly get reused.

- d) With information redundancy additional information is being used e.g. checksums that verify that data are correct with less performance penalty than time and software redundancy.

The main problem of fault tolerance is adjusting the number and the kind of redundant system resources. We have again a resource management problem. Partial reconfiguration can help in the correction of SEUs on the configuration memory as we can see in [72]. We use it to correct efficiently SEUs on application-level functionality. Only a small amount of system's processes are critical enough to need fault tolerance.

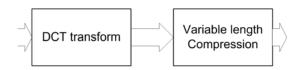

Figure 13. Typical audio/ image commercial application

For example in commercial applications we frequently find computational requirements for data-oriented algorithms e.g. DCT and control oriented e.g. compression algorithms as shown in Figure 13. A fault in the DCT algorithm is insignificant but a fault on the compression algorithm is critical since it may cause loss of synchronization and system failure. If both the DCT and the compression algorithms can be accelerated on a reconfigurable hardware component which one should get accelerated? The answer is not straightforward since the two algorithms share a common data stream. If we accelerate the DCT algorithm and choose to have time redundancy for compression we may end up with a bandwidth that the latter can't handle. If we provide hardware fault tolerance to the compression algorithm the DSP algorithm may be unable to provide the appropriate bandwidth to the compression algorithm. Carefully tuned dynamic resource management switching

between hardware and time redundancy gives the best solution in this scenario and most real-life applications are like this.

Core Services use the run-time mapping mechanism to provide fault tolerance with an optimum way at a given time. The most important advantage is that they achieve this without any development effort. Fault tolerance is being provided by the framework and can also be used at design time for debugging purposes i.e. verifying the equivalence between hardware and software implementations. Each service call is being invoked with a redundancy parameter which specifies how many voting results (up to 16) should agree to accept a result. These voting results are being obtained by executing the service in the fastest combination of (hardware or software) service providers available at that time as we can see in Figure 14.

Figure 14. Fault Tolerance with Core Services

The results of a Service may be large vectors and comparing them would be a waste of time but most importantly waste of precious bus's cycles in order to collect them in the core where voting takes place. In Core Services only one Provider returns the full set of results and a checksum while the others return only their checksums saving significant bus bandwidth. The kind of checksum is not specified by Core Services and this allows significant application specific optimizations. In a software dominated platform the use of a Linear Feedback Shift Register (LFSR) for checksums would require significant computational resources. Additionally by comparing only the checksum we may be able to save time by not performing operations that produce invariant results in respect to the checksum. For example in many encryption algorithms the final step is a scrabbling of the output parameters. If the checksum is a simple addition this last step is unnecessary because the sum of numbers is invariant to their order.

Figure 15. Out of order fault tolerance with Core Services

Finally the processor may go on with its computations as soon as the first full result arrives assuming that it's correct. Checksum comparison may take place latter when all Services complete and in most of the cases it will be correct giving near non-fault tolerance performance (see Figure 15).

### 2.3.4 Platform based design

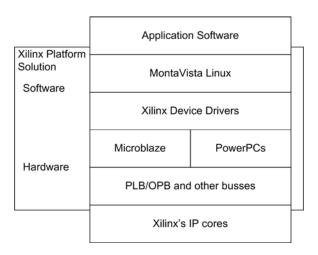

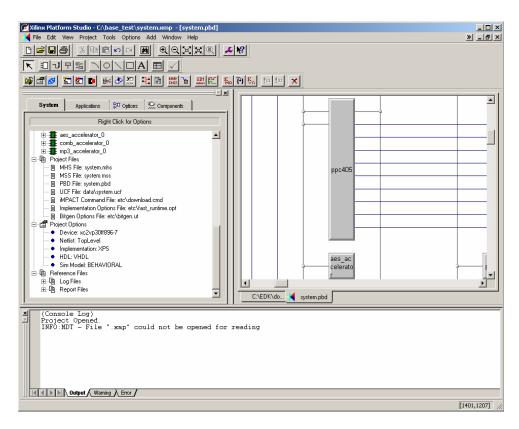

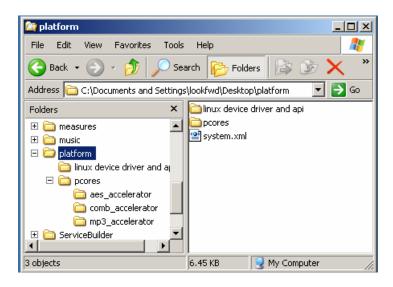

Platform based design promises to increase productivity, decrease time to market and development costs by re-using out-of the self pre-verified components within a platform framework [73]. At this moment platform based design as provided for example by Xilinx via Xilinx Platform Studio (EDK) is a good step towards these promises. You can easily develop a complex system consisting of IP cores provided by Xilinx and its partners. For example for the XUP Virtex II Pro platform (see Appendix A) one could easily connect two PowerPC cores with RAMs and other peripherals by using the CoreConnect hierarchical bus. It's quite simple to create the hardware and basic software drivers for this platform by using XPS giving a kick-start for developing new applications (see Figure 16). There is also the option to use MontaVista linux which offers all the software friendliness of Linux and device drivers for most of the essential peripherals of the platform.

Figure 16. Platform based design with Xilinx Platform Studio and MontaVista linux

Still, the question remains: Why to use Xilinx's Platform Studio when there exist more efficient processors with equivalently large set of peripherals and at least equally good software support in a less power hungry and cheaper application oriented System-on-Chip like Philips' Nexperia. The answer is reconfigurability. Xilinx's flow supports the addition of custom hardware accelerators who offer the potential of unbeatable acceleration.

But how well does this platform's flow supports its only competitive advantage? The answer is not so well. There is only one wizard that allows the creation of a template custom hardware and software peripheral. In fact a developer for this platform can't avoid studying the underlying PLB/OPB busses, work explicitly to convert the endianess's of the signals and resolve a lot of handshaking problems. From software side a template is provided that slightly abstracts the underlying bus. A custom driver has to be developed in order to transfer data to the custom core and get responses back. Of course there is no support at all for Linux for which someone has to redevelop a complete device driver in order to access the peripheral. After all this effort what does someone have? A component that is very tightly coupled to the platform. If the communication infrastructure changes e.g. turn to NoC then the hardware will

have to be modified again or at least get "wrapped" possibly loosing some of its performance. The device drivers also will change. Hopefully if the device driver is well written, user applications won't need modifications. The worst of all from a business point of view is that all these IPs are very platform specific and for example for sophisticated components it would be very expensive to switch from e.g. Xilinx to Altera. Obviously every company wants to be vendor independent in order to take advantage of vendor's competition so it's forced to implement its own abstraction over these platforms for its IPs.

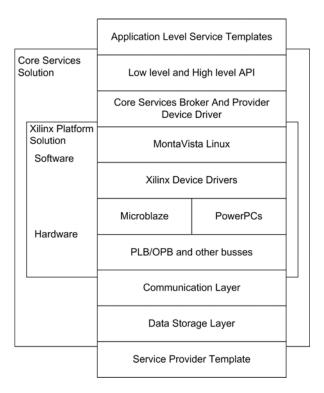

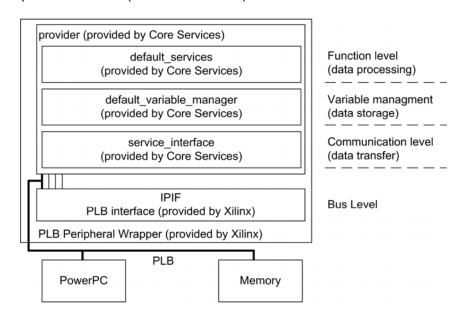

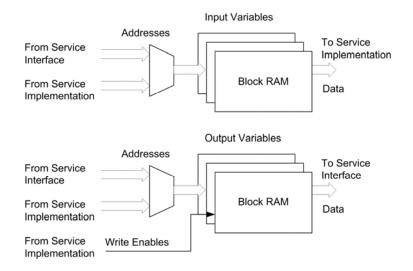

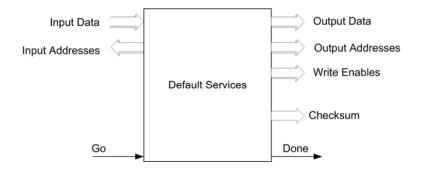

Figure 17. Core Services' stack over Xilinx's Platform

Web Services deal with machine-to-machine interoperability and Core Services do the same on a platform-to-platform level. They achieve this by adding one software and two hardware abstraction layers over Xilinx's flow. From the hardware layer the communication layer hides completely the bus and Core Services' communication protocol and provides an interface suitable for memory-like (slaves) components. On top of it that the data storage layer holds the data in the form of one independent RAM for each variable used for a service provider. It provides an interface that is suitable for processor-like components (masters). On top of it lies the actual Service Provider which can access each variable independently increasing the maximum achievable throughput and thus minimizing the computational time. By having two layers of abstraction we support two stage reconfiguration [29]. Implementation at the top abstraction level is very simple. For example for the calculation of a mathematical expression like  $\overrightarrow{out} = \overrightarrow{in1} + \overrightarrow{in2} \cdot \overrightarrow{const}$  an implementation could be almost as simple as this:

```

out[count] <= in1[i] + in2[count] * const[count];

outwe[count] <='1';</pre>

```

Passing the variables, returning the parameters and communicating with the software is being handled by the middle layers.

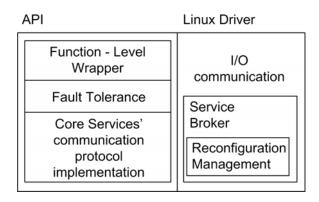

From software side there are similar improvements over the Xilinx's platform. A Linux Device Driver that provides access to the Service Broker and the Service Providers is provided. Each of them is being accessible as a single device in the /dev/ directory. On top of that the low level and high level API are provided to the applications. The low level API provides more flexibility to the application developer in terms of performance but requires better knowledge of the Core Services' functionality. The high level API uses the low level API and gives the developer a completely abstract remote procedure call interface. No knowledge of Core Services internals is required at this level. For example a call using the high level API would be as simple as this:

```

void funDefaultMAC(int * in1, int * in2, int* out) {

// Default (software) implementation

for (int i = 0; i < 10; i++)

out[i] = in1[i] + in2[i] * const[i];

}

...

csMAC(funDefaultMAC, in1, in2, out, NO_REDUNDANCY);</pre>

```

As you can see, there are no hardware references at all. This abstraction level is much more platform independent than a traditional call like this:

```

send_peripheral_data(REQUEST, BROKER_ADDRESS);

p = get_peripheral_data(BROKER_ADDRESS);

for (int i = 0; i < 10; i++)

send_peripheral_data(in1[i], PERIPHERAL_BASE_ADDRESS[p]);

...</pre>

```

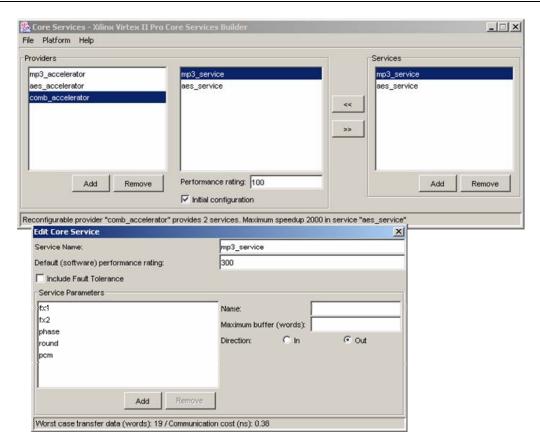

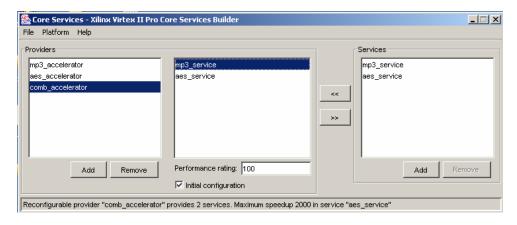

Figure 18. Core Serices Builder: The Core Services' GUI

As described in [73] with the ever-increasing pressure of time to market infrastructures and tools must be developed in synchrony with design methodology. Core Services' methodology is being accompanied by tools and infrastructure including Core Services Builder (see Figure 18), a user friendly interface via which one can customize Core Services and Service providers and have all the hardware and software created automatically. The tool provides interactive information for the communication costs and performance gains in order to aid designer's decisions.

### 2.4 Related Work

Several other researches have attempted to solve some of these problems with approaches similar to Core Services. We will present the most similar works and highlight the points where Core Services differ.

Object oriented methodology has the idea of polymorphism which means that a function call may map to different implementations according to the class of the object that it belongs to. In [74] they expand their previous [75] ASIP (application-specific instruction set processor) methodology to use the NoC to dispatch with zero overhead virtual methods to hardware or software implementations. They do not provide dynamic resource management as Core Services.

In [76] they present a Java based abstract stream decoder technology for reconfigurable hardware. They lack many of the strong semantics of Core Services. In the very interesting and somehow technical [77] transparent management of reconfigurable hardware or software components is being proposed. They use CAN bus for communication. "Run-time optimizations" and "partial run-time reconfigurable modules" are left for "future versions".

The work in [78] has many similarities with our by referring to Common Object Request Broker Architecture (CORBA), Java Remote Method Invocation (RMI) and having an "IP Core Lookup Service" which instantiates objects and decides reconfigurations which is similar to our object broker. They also use objects to abstract hardware which is not quite suitable for reconfigurable hardware and it naturally leads them to use ad-hoc methods for serialization in order to aid relocation. Although they claim that their methodology improves performance they have no mechanism to guarantee it as they don't consider computation or communication costs at all. They assume hardware implementations are faster than software without considering the communication costs and they implicitly assume that all hardware accelerators provide the same speedup for a functionality which is true only if the same implementation is being used. Core services are stateless which simplifies both hardware and software and makes relocation unnecessary. They also provide reconfiguration mechanism and run-time mapping which optimize for performance and guarantee acceleration via the performance deadline.

On the other hand in [79] they present a heuristic similar to ours (see section 3.2.3) for computation and communication costs and they use it to map tasks to PEs. All the resource management is being handled by a single master processor and although the technique is supposed to target on multi-processor systems they describe a one-master-many-slaves architecture. Core Services Phase I mechanism (see section 3.2.1) allows multiple masters to gain access to accelerating resources.

# Chapter 3. Core Services methodology, mechanics and implementation

### 3.1 The methodology

Core Services are meant to be the equivalent of web services optimized for on chip communication. The steps of the Core Services methodology are the following:

# Step 1. Profile the system and sort its functions by the total amount of time spent on each.

By starting this methodology it is assumed that there exists a functional software prototype of the system. By profiling we identify the functions that consume most of the time. Obviously this is the first place to look optimizing system's performance.

### Step 2. Decide if they are suitable for hardware implementation.

We give a detailed description on section 3.4 on how to decide if a function is suitable for hardware implementation.

# **Step 3.** Replace with service calls and provide default service implementation. Assuming that the platform has a Core Services' implementation this is as easy as modifying slightly the original function and calling it via Core Services' wrapper.

### Step 4. Test the software only implementation on the platform.

At this level we can verify that the system works correctly after adding the Core Services' functionality by using the default software service implementations.

# Step 5. Calculate the estimated savings of making a hardware accelerator for this function. If constrains aren't yet met, accelerate more functions.

Communication cost for the given platform can be accurately estimated at this stage because the length of the call and return values are known. A hardware engineer can give estimates on the speed of a hardware implementation of a certain functionality. As a result we can know in such an early stage if the savings suffice to meet system's constraints. If not we can turn more functions to Core Services. If hardware implementations can't or needn't be provided latter the system will still be functional.

### Step 6. Create hardware test data.

By running the application as described on the previous step, we can create as many test data as required with an automatic or semi-automatic way. Time consuming system-level simulations are being avoided by using Core Services.

# Step 7. Create hardware instance of Core Service using automatically generated service stack and verify with the test data.

Hardware templates generated by Core Services' fingerprint and test data can significantly ease the implementation of the hardware component. Manual optimizations on the templates can be performed if time allows.

# Step 8. Calculate the actual savings of making a function Core Service. If the constrains aren't yet met, create more hardware components or optimize more the existing ones.

At this stage we have actual data for the time it takes the hardware to complete the service. Precise evaluation of the savings can be performed.

### Step 9. Test the software/hardware implementation on the platform.

Now system level testing can be performed. Testing can be eased by the fault tolerance facilities of Core Services. Both software and hardware instances are being called and if the checksums of the results aren't the same warnings may be issued.

### 3.2 Core Services' communication protocol and algorithms

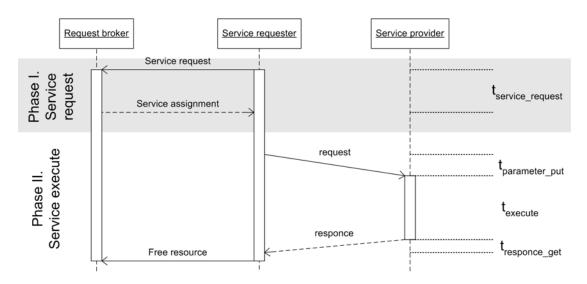

Figure 19. Core Service transaction details

Figure 19 shows a Core Service transaction. We will present the details of the communication protocols and the algorithms that are involved in a Core Service transaction.

### 3.2.1 Phase I. Service request

### 3.2.1.1 Service Request

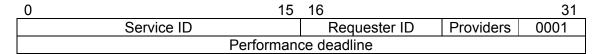

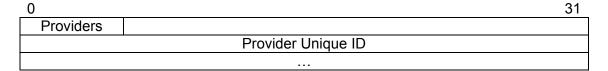

Phase I of a service transaction is the service request. In this phase, the requester contacts a request broker and asks for service. The form of a request packet can be seen in Figure 20.

Figure 20. Service request packet format

The MSB of the first word is 1 to denote a service request packet. The fields on a service request packet are the following:

#### 1. The service ID of the service requested

Each service is described by its unique ID. This is system-level unique and is assigned at design time. It is 16-bits long giving a maximum of 65536 services.

### 2. The ID of the service requestor

The ID of the service requestor is needed in order to return the response to the requester and calculate inter-core costs. For example the communication costs over NoCs may depend on the distance between the cores. This is 8-bit field so it supports up to 256 service requesters.

### 3. The number of service providers requested

The number of service providers may seem unnecessary but its' necessary to support fault tolerance. A single request may require more than one service providers for example two for fault tolerance in a moderate faulty environment. 4-bits are reserved for this number giving a potential of 16 service providers per request. If an application that requires fault tolerance is run on a platform that doesn't support it the performance will be reduced compared to another platform that supports it because of software simulation of multiple calls.

### 4. The performance deadline to be met

The performance deadline is the number of clock cycles that the service requester estimates it will take itself to complete this service. This is being used to provide a run-time adjusted threshold to the service broker in order to decide if it's reasonable to assign a service provider to this request.

In fact the performance deadline is just a metric and it isn't bound only to time. It could be for example a combination of energy and time. In most cases, better time performance means also better energy performance [80-82] so it's reasonable to use time as a metric. The easiest way to statically predict this number is by profiling. If a big variance in execution time is expected, the service requestor should multiply it by a load factor dependent, for example, on the number of active threads/processes in order to reflect its load. In might also be useful to under-estimate slightly if it's more important to off-load the requester in order e.g. to provide better behaviour in unpredictable real-time events.

### 3.2.1.2 Service assignment

The response by the service broker can be seen in Figure 21.

Figure 21. Service assignment packet format

The fields on a service assignment packet are the following:

#### 1. Number of providers

This is the number of providers that have been allocated to the requester for this request. It may be less than the number of service providers requested e.g. zero if no such service is available or none meets the performance deadline. This field is 4-bits long as the respective request field.

#### 2. Provider ID

A list with unique identifiers for the specific service follows. These ID's are being used to send the parameters as described bellow. The meaning of these ID's is platform depended and may be for example base addresses, IPs or port numbers.

### 3.2.1.3 Why is a service broker needed?

A service broker is needed at least as a means of having a central repository of services and their availability status. An alternative to this would be to have a completely ad-hoc system in which each request would be broadcasted to the 'market' of service providers, they should respond by bidding for the service request and the best offers would be accepted. No matter how nice this scenario sounds it

has important performance and power drawbacks. The service request gets broadcasted to all the service providers, even those that may not provide a service. Additionally a large number of bids would have to be communicated even from providers that have non chance of being accepted. Obviously all these end up in a waste of performance and power. The existence of the central 'marketplace' of the service broker saves all these resources.

### 3.2.1.4 Why does a service broker make the service assignment?

Alternatively the request provider could be given a complete list of services and metrics let decide itself. Apart from the increased interface complexity and the communication overhead such an implementation there are other important drawbacks. The external broker DEDICATES the providers to the requesters. If this dedications didn't hold true in a multi-threaded but even more in a multi-processor environment a lot of collisions would occur. Requesters of the same Core Service would reasonably try to allocate the best resource. The first one checks if it's free and locks it with an atomic operation. The others check with failure and either look for an alternative service provider or wait until the first one completes and take their turn. Obviously this is too much overhead for an embedded system. It is much better to have a central locking mechanism that manages the service providers. This is true for small number of service requesters. If there were a lot of service requesters the availability of the broker would become an important bottleneck. However a service broker can easily be implemented by multiple cores using a shared memory for their synchronization. Obviously the decision of making the assignment on the service broker scales well even in much larger systems.

### 3.2.2 Phase II. Service execute

### 3.2.2.1 Parameter passing

Phase II of a service transaction is the service execution. In this phase, the requester communicates directly with service provider to pass the parameters and get the response.

The fact that the service provider doesn't have to retain its state between two subsequent accesses simplifies both hardware and software. We can't be guaranteed that two subsequent service requests are going to be serviced by the same service provider. As a result, the state should be transferred from one service provider to another which is generally impossible because different service providers may be incompatible of each other. Even in systems where only one service provider exists for each service a request from another thread may interleave between two subsequent requests from a thread resulting in service corruption.

It may seem as a waste of scarce system resources that we write data from the main memory to the hardware accelerator and we should prefer a shared memory model where data are being passed by reference instead. Our decision is safer for several reasons:

- 1. Data may not be in the main memory but in a local cache.

- 2. Even if you move data by reference, the service provider still will have to read them, so you don't save the reading part.

- 3. Core Services give that ability implicitly. One can pass a pointer as variable and a service provider capable of reading the main memory will use it to read the data. In this case one must be careful a) to give a valid physical memory location which may be different from a pointer's virtual address b) to resolve cache coherence and memory ownership issues that may arise.

The ability to have variable sized variables is important in order to support functions with strings as parameters.

Core Services' parameters and responses are only arrays of 32bit words. This is done because it's only meaningful to run a service on another processor if it takes considerable amount of time. Apart from random number generation and some rare cryptographic applications with extremely high complexity large amount of time means large amount of data as well.

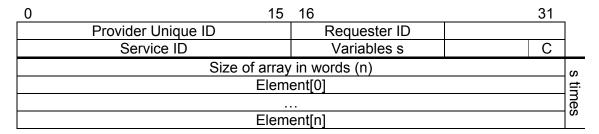

Figure 22. Request packet format

The format of a request packet can be seen in Figure 22. It contains provider unique ID, the Requester ID that will be used to receive the response, the service ID requested and the number of variables (parameters) that are being passed to the service. The (C)hecksum flag tells the provider if a full reply should be send or just the checksum for each variable. Then s parameters follow each one prefixed by its size in words and then the words of the data in sequence. At the end of this packet, the computation begins.

### 3.2.2.2 Response getting

The service provider sends back the response. This may be done by pulling or by pushing depending on the platform i.e. the requester may read the data from the provider or the provider may send the data to the requester. In the former case, there must be a mechanism to tell the requester that the computation was completed and the data are ready. This may be done by polling or more efficiently by an interrupt if the platform supports it.

| 0                          | 15 16              |              | 31 |   |   |   |

|----------------------------|--------------------|--------------|----|---|---|---|

|                            | Provider Unique ID | Requester ID |    |   |   | Ī |

|                            | Service ID         | Variables s  |    | S | C |   |

| Size of array in words (n) |                    |              |    |   |   |   |

| Element[0]                 |                    |              |    | S |   |   |

|                            |                    |              |    |   |   |   |

| Element[n]                 |                    |              | es |   |   |   |

|                            | Checksum           |              |    |   |   |   |

Figure 23 Response packet format

A similar format with the request packet is being used for response packets as shown in Figure 23. The only difference is the existence of a checksum that is being used if the service supports fault tolerance. If the S flag is set, then the packet contains checksums. If the C flag is set, then the packet contains only the checksum and not the variables themselves. Bare packet's size and thus communication cost is significantly reduced. The kind of checksum is platform dependent and may be more or less software-friendly.

#### 3.2.2.3 Free resource

A free resource packet (see Figure 24) is being sent to the service broker in order to notify that the providers have been freed and can get reused.

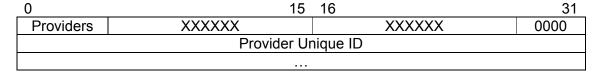

Figure 24. Free resource packet format

The MSB of the first word is 0 to denote a free resource packet. The fields on a free resource packet have similar meaning to the ones of resource assignment packet (see section 3.2.1.2).

### 3.2.3 Mapping algorithm

Mapping of the requests to the service providers is being implemented by the object broker. There are many different ways to do them but the more intuitive way is the following one that is actually being suggested by the Core Services' infrastructure.

A request provides the following data: The number of providers requested  $n_p$ , the deadline  $t_d$ , the service ID S and the requester ID  $ID_r$ . We can see in Figure 19 four times that characterize a transaction:  $t_{service\_request}$ ,  $t_{parameter\_put}$ ,  $t_{response\_get}$ ,  $t_{execute}$ . The  $t_{parameter\_put}$  and  $t_{response\_get}$  can be merged to a single value, the communication time:  $t_{comm} = t_{parameter\_put} + t_{response\_get}$ .

The problem is that we have a set of service providers SP from which only  $ASP \subseteq SP$  are available at a given time and each providing a set of available services  $A_{sp}$  and we want to return a subset  $X \subseteq ASP$  of  $a_p \le n_p$  service providers that provide the service  $S \in A_x, \forall x \in X$ , have minimum cost  $c(x) \le c(s), \forall x \in X, \forall \{y \in SP \mid y \not\in X\}$  and less than the performance deadline  $c(x) < t_d, \forall x \in X$ . We would like to have a fast algorithm because it affects the  $t_{service\_request}$  which is a pure overhead in service call.

The easiest way to find the best X is to maintain a list with one node for each available service provider which has a list with one node for each available service  $A_{sp}$ . This algorithm has a worst case complexity of  $O\left(size\left(ASP\right)\cdot max\left(size\left(A_{sp}\right)\right)\right)$  which may be bad for large number of service providers or available services.

```

bestcost \leftarrow \varnothing \\ X \leftarrow \varnothing \\ \text{for each service provider x in } ASP \text{ do} \\ \text{for each service } s \text{ in } A_x \text{ do} \\ \text{if } (s = S \text{ and } c(x) < t_d \text{ and } c(x) < bestcost(t), \forall t \not \in X) \text{ then} \\ \text{if } \left(size(X) > n_p\right) \text{ then} \\ \end{cases}

```

```

\texttt{find\_and\_remove(worst\_element($X$\,))} \texttt{end if} \texttt{bestcost} \leftarrow \texttt{bestcost} \cup \texttt{c(x)} \texttt{X} \leftarrow \texttt{X} \cup \texttt{x} \texttt{end if} \texttt{done} \texttt{done}

```

Another algorithm which has much better performance can be implemented by using hash tables of services  $h_s$  with each entry containing a sorted list of active service providers  $l_{ASP}$  for that service. This is a very fast algorithm that gives very fast access time O(1) but requires much more memory and considerable housekeeping effort to keep the structure up to date when availability of services changes.

$$X \leftarrow h_s[S][1...n_p]$$

Both algorithms are useful and there are a lot more algorithms in the middle between them. The first one is good for hardware implementation or in a processor with limited amount of memory or in a system that has a small amount of service providers and services per provider. The second one is more suited to large systems with many service providers and services and with taught deadlines that can't afford an increased  $t_{service\_request}$  but can afford the extra memory needed to keep a well organized registry.

The main problem that we set aside until now is the calculation of the cost for executing a Core Service in a service provider c(x). There are two dangers. The one is to oversimplify and reduce the efficiency of run-time mapping, the other is to over-analyze and reduce the performance benefits because of the computational overhead of calculating the cost. We want to include the computational and the communication costs.

The computational costs can be represented as a  $n_s \times n_p$  matrix  $c_c$  of the average clock cycles of execution where  $n_s$  is the number of services,  $n_p$  is the number of providers. Run-time variable load factors can be expressed by a vector lf of  $n_p$  elements. lf(i) = 1 when the processor i is average loaded, < 1 if it's under-loaded and > 1 if it's overloaded. The computational cost including loading is  $c_{comp} = c_c \cdot diag(lf)$ .

The communication cost can be approximated with an average bandwidth  $bw_{i,j}$  in clock cycles/word from service requester i to service provider j. The number of words per service  $w_s$  includes parameter passing and response getting and is known at design time. The total communication cost  $c_{comm} = w_s \cdot bw_{i,j}$  is known at design time and can be represented with a  $n_s \times n_r \times n_p$  matrix. Note that if the communication costs present large variance and the average bandwidth  $bw_{i,j}$

induces large errors we can easily add a run-time variable load factor to this model as in the case of computational costs.

The total cost  $c(x \mid r, s, lf)$  for a given service s, requester r and load factor lf, can be calculated with three array accesses and a multiplication. It is  $c(x \mid r, s, lf) = (c_{comp})_{s,x} + (c_{comm})_{s,x,r}$ . If these two matrixes  $c_c$  and  $c_{comm}$  are set, Core Services are ready to work.

For example in a system with 2 service requesters and 3 service providers for 2 services. Given a run-time load factor  $lf = \begin{pmatrix} 1.1 & 1 & 0.8 \end{pmatrix}$  and a computational cost matrix

$$c_c = \begin{bmatrix} 30 & 20 & 70 \\ 40 & 50 & 12 \end{bmatrix}$$

we have a total computational cost of

$$c_{comp} = c_c \cdot diag(lf) = \begin{bmatrix} 33 & 20 & 56 \\ 44 & 50 & 9.6 \end{bmatrix}$$

For given inter-processor bandwidth  $bw_{i,j} = \begin{bmatrix} 1.3 & 1.3 & 2 \\ 1 & 1 & 1.3 \end{bmatrix}$  and  $w_s = \begin{pmatrix} 10 & 20 \end{pmatrix}$  words per service we have a communication matrix:

$$c_{comm} = \left( \begin{bmatrix} 13 & 13 & 20 \\ 10 & 10 & 13 \end{bmatrix}, \begin{bmatrix} 26 & 26 & 40 \\ 20 & 20 & 26 \end{bmatrix} \right)$$

The total cost of services is:

$$c(x \mid r, s, lf) = (c_{comp})_{s,x} + (c_{comm})_{s,x,r} = \begin{bmatrix} 46 & 33 & 76 \\ 43 & 30 & 69 \end{bmatrix}, \begin{bmatrix} 70 & 76 & 49.6 \\ 64 & 70 & 35.6 \end{bmatrix}$$

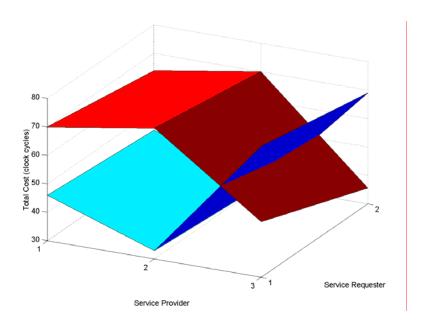

Figure 25. Total cost for two Core Services

As we can see in Figure 25 the cost of the two Core Services varies not only with the service provider but also with the service requester.

### 3.2.4 Reconfiguration management

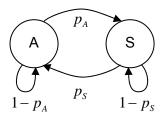

Given that we have a reconfigurable service provider able to provide n services  $S_1...S_n$  and currently it's configured to provide service  $S_c$ . Each service gives a corresponding speedup of  $s_1...s_n$  each time it executes and in the last frame requests we have  $n_1...n_n$  requests for each service. The reconfiguration penalty is  $t_p$  during which it can't provide any service.

The potential speedups in the last frame requests for the i-th service are  $s_i \cdot n_i$ . There is a best service  $S_b$  for the last frame for which  $s_b \cdot n_b \geq s_i \cdot n_i, \forall i \neq b$ . If there are more than one best services with equal potential speedups we select as  $S_b$  the current service  $S_c$  if it belongs to that set otherwise a random service from that set and we continue.

If the best service  $S_b$  is the one that we already run  $S_c$  then there is nothing to do. We have an optimum solution. If not then we have to examine the opportunity cost, "the most valuable forgone alternative". That's  $s_b \cdot n_b$ , the potential speedup for our best service. But we are already having a profit of  $s_c \cdot n_c$  because of the chosen service  $S_c$ . So the actual loss is:  $t_{loss} = s_b \cdot n_b - s_c \cdot n_c$  and it has units of time. Assuming that we will have the same profile of requests in the near future, If we invest  $t_p$  time of inactivity we will gain a future profit increase of  $t_{loss} = s_b \cdot n_b - s_c \cdot n_c$  per  $t_{frame}$ . We just have to define a threshold time  $t_{th}$  in the order of  $t_p$ . If the accumulated  $t_{loss}$  for the same  $S_b$  exceeds  $t_{th}$  we decide a reconfiguration  $S_c \leftarrow S_b$ . The algorithm has a complexity of O(n) because of argmax and is as follows:

```